Karena masalah dengan Intel® FPGA Power and Thermal Calculator (PTC) di Intel® Quartus® Prime Edisi Pro Versi 20.3 dan sebelumnya, Anda mungkin melihat galat ini bahkan jika masih ada pin yang tersedia ketika pin input diferensial digunakan dan tegangan VCCIO dari semua bank I/O bukan 2,5V di Intel® Stratix® perangkat 10.

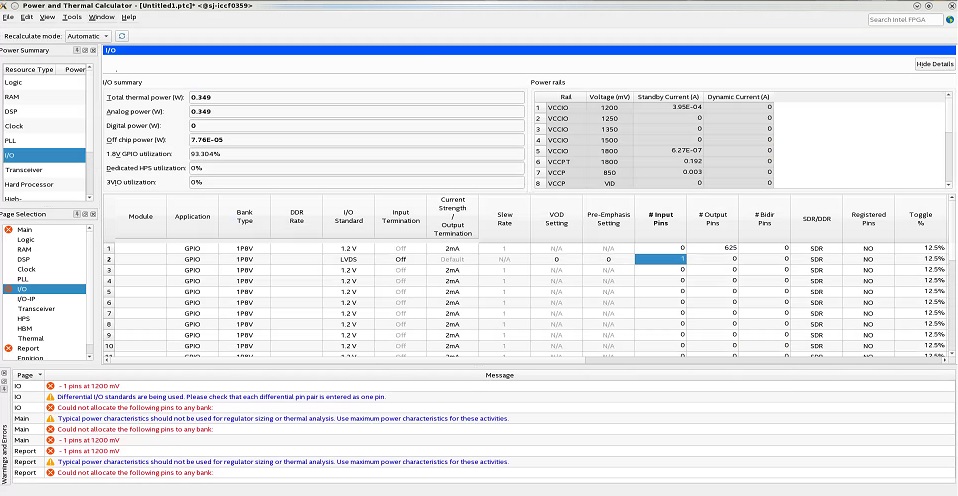

Berikut adalah contohnya.

Perangkat: 1SG280H

Paket: F50

Jumlah I/O pengguna: 672

Jumlah bank I/O: 14

Jumlah pin pra bank I/O: 48

Penggunaan I/O pengguna:

Keluaran 1,2 V * 625 pin

Input LVDS * 1 pasang

Dalam hal ini, karena 625 pin digunakan untuk output 1,2 V, tegangan VCCIO dari 14 bank I/O adalah 1,2 V.

Input LVDS didukung oleh VCCPT, bukan VCCIO. Jadi sepasang input LVDS harus dapat ditugaskan ke pin yang tersisa, tetapi PTC salah menampilkan galat seperti yang ditunjukkan pada gambar berikut.

Anda dapat mengabaikan galat ini dengan aman.

Masalah ini telah diperbaiki dimulai dengan Intel® FPGA Power and Thermal Calculator (PTC) pada Perangkat Lunak Intel® Quartus® Prime Edisi Pro versi 21.3.