Saat menghasilkan frekuensi clock output dengan C-counter melebihi 512, cascading counter pasca-scale diterapkan. Jika Anda menghasilkan MIF/HEX dari ALTPLL Intel® FPGA IP di mana penghitung C melebihi 512, penghitung C bertingkat tidak didukung. Setelah konfigurasi ulang, Anda mungkin melihat bahwa frekuensi clock output salah.

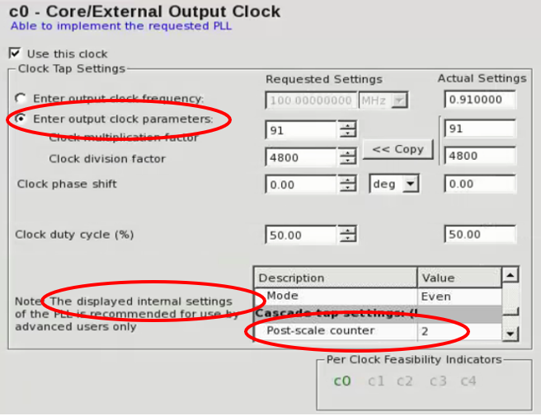

Aktifkan Parameter clock keluaran Enter di Intel® FPGA IP ALTPLL dan sesuaikan parameter clock output secara manual. Pastikan bahwa penghitung C tidak melebihi nilai 512 dan pengaturan internal tidak menyuntikkan cascading counter post-scale sebelum menghasilkan file MIF/HEX seperti yang ditunjukkan pada Gambar 1.

Gambar 1.

Sebagai alternatif, cascading PLL dalam mode normal atau langsung melalui jaringan Global Clock (GCLK) dapat digunakan untuk mencapai frekuensi clock output yang diinginkan.