Karena masalah pada Perangkat Lunak Intel® Quartus® Prime Edisi Pro v21.4, desain Intel® FPGA IP F-tile PMA/FEC Direct PHY yang berisi transivator FGT atau FHT mungkin salah menunjukkan kegagalan waktu yang terkait dengan soft reset controller (SRC).

Karakteristik dari kegagalan waktu ini adalah bahwa peluncuran atau jam kait akan terdaftar sebagai src_divided_osc_clk. Clock lainnya (baik jam kait atau jam peluncuran) akan menjadi jam yang berbeda.

Anda mungkin juga melihat bahwa kendur yang dilaporkan adalah angka negatif yang sangat besar, berdasarkan urutan -90 ns.

Contoh kegagalan waktu ini adalah sebagai berikut:

Contoh Kegagalan Waktu 1

Dari Node: IP_INST[0].hw_ip_top|dut|eth_f_0|sip_inst|sip_freeze_tx_src_reg[0]

Ke Node: eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl_sync|sip_freeze_tx_SRC_sequence_inst[18]|din_s1

Jam Peluncuran: reconfig_clk

Jam Kait: src_divided_osc_clk

Model Tunda: pengaturan 2_slow_vid2_100c : -1,474 tahan : 0,027

Model Tunda: pengaturan 2_slow_vid2b_100c : -1,574 tahan : 0,167

Model Tunda: pengaturan MIN_fast_vid2a_0c : -1,193 tahan : 0.216

Model Tunda: pengaturan MIN_fast_vid2a_100c : -1,304 tahan : 0,186

Model Delay : pengaturan MIN_fast_vid2_100c : -1,244 hold : 0,093

Contoh Kegagalan Waktu 2

Dari Node: eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl|dp_sip_rx_aib_control_select[19]

Ke Node: eth_f_hw__tiles|z1577a_x0_y0_n0|hdpldadapt_rx_chnl_19~pld_rx_clk1_dcm.reg

Jam Peluncuran: src_divided_osc_clk

Jam Kait: IP_INST[0].hw_ip_top|clkdiv2_pll_inst|altera_iopll_0_outclk0

Model Tunda: pemulihan 2_slow_vid2_100c : -90,597 penghapusan : 0.244

Model Tunda: pemulihan 2_slow_vid2b_100c : -90,756 penghapusan : 0,446

Model Tunda: pemulihan MIN_fast_vid2a_0c : -90,063 penghapusan : 0,535

Model Tunda: pemulihan MIN_fast_vid2a_100c : -90,241 penghapusan : 0.316

Model Tunda: pemulihan MIN_fast_vid2_100c : -90,057 penghapusan : 0,076

Masalah ini telah diperbaiki berawal dari Intel® Quartus® Perangkat Lunak Prime Edisi Pro v22.1.

Untuk mengatasi masalah ini di Intel® Quartus® Perangkat Lunak Prime Edisi Pro versi 21.4 atau sebelumnya, jalur gagal yang terkait dengan kontroler reset lunak dapat diabaikan dengan aman.

Namun, Jika Anda memilih untuk memperbaiki kegagalan waktu yang salah ini sehingga tidak dilaporkan, ikuti langkah-langkah berikut:

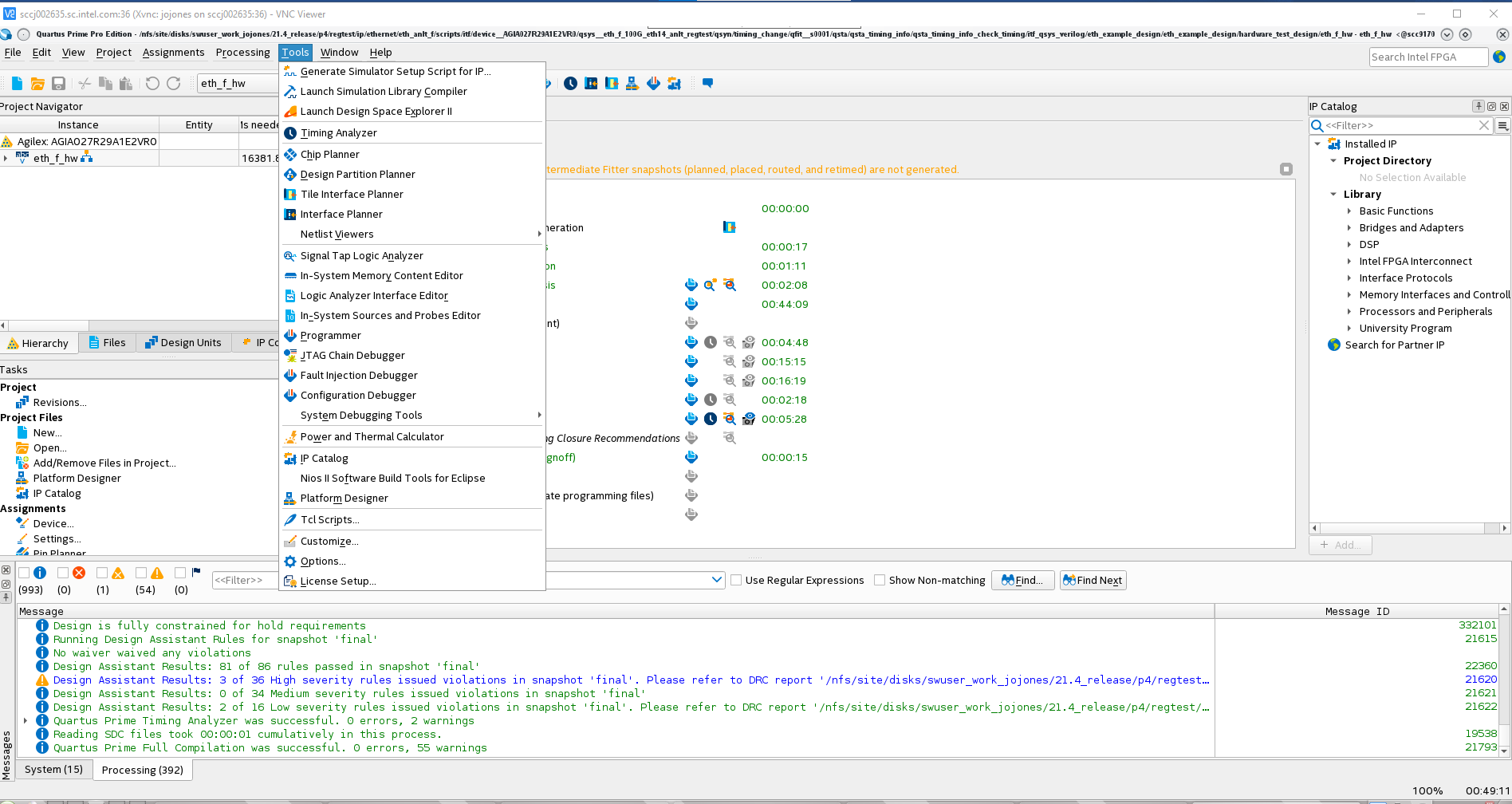

- ) Setelah Anda telah mengkompilasi desain Anda di Intel® Quartus® Prime Software, luncurkan Penganalisis Waktu dari menu Alat .

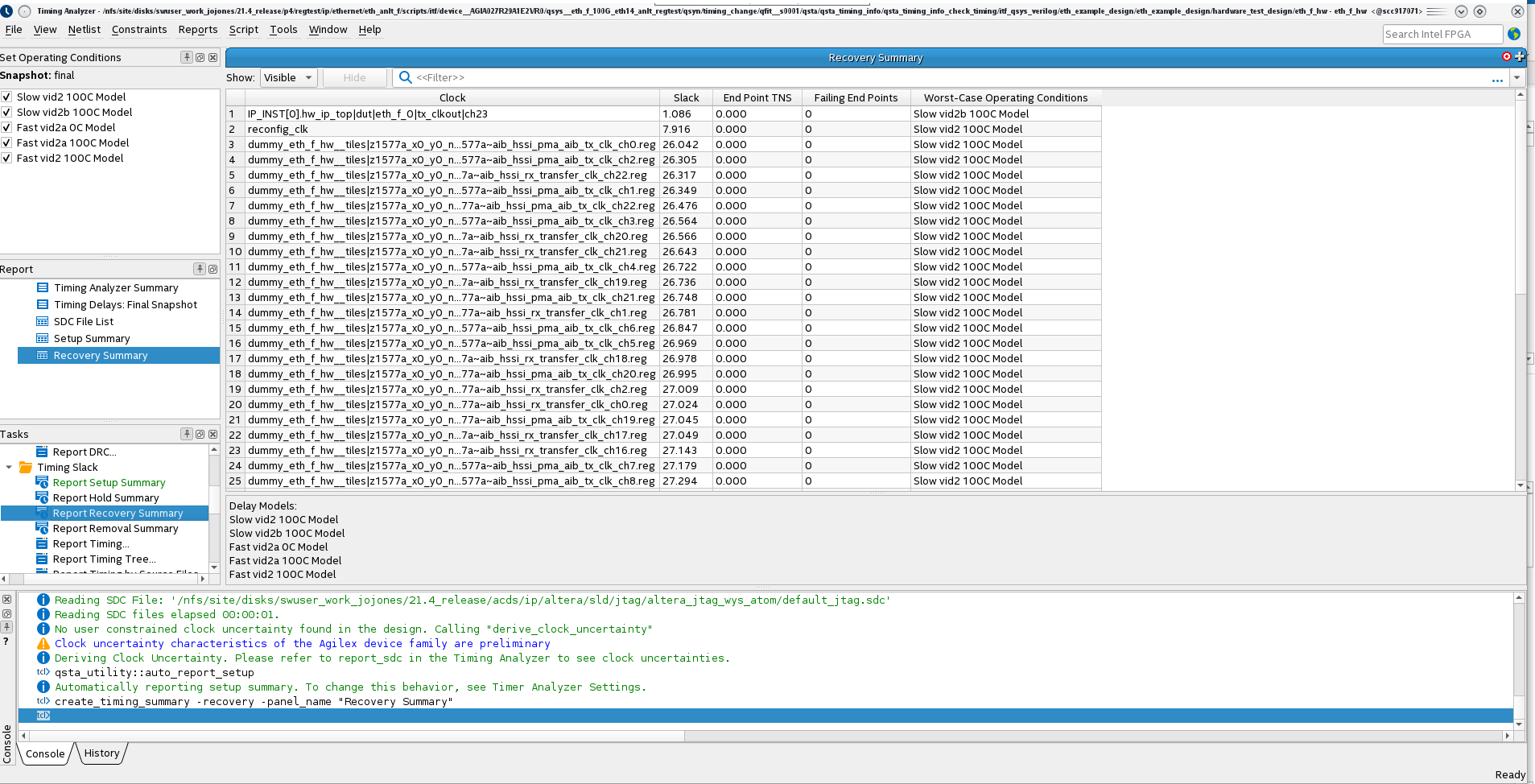

- ) Setelah Timing Analyzer membuat netlist waktu, Menghasilkan berbagai laporan waktu termasuk laporan pengaturan waktu dan laporan waktu pemulihan.

Dalam hal ini, meskipun jalur palsu tidak dibatasi, penganalisis waktu tidak melaporkan galat waktu apa pun.

-

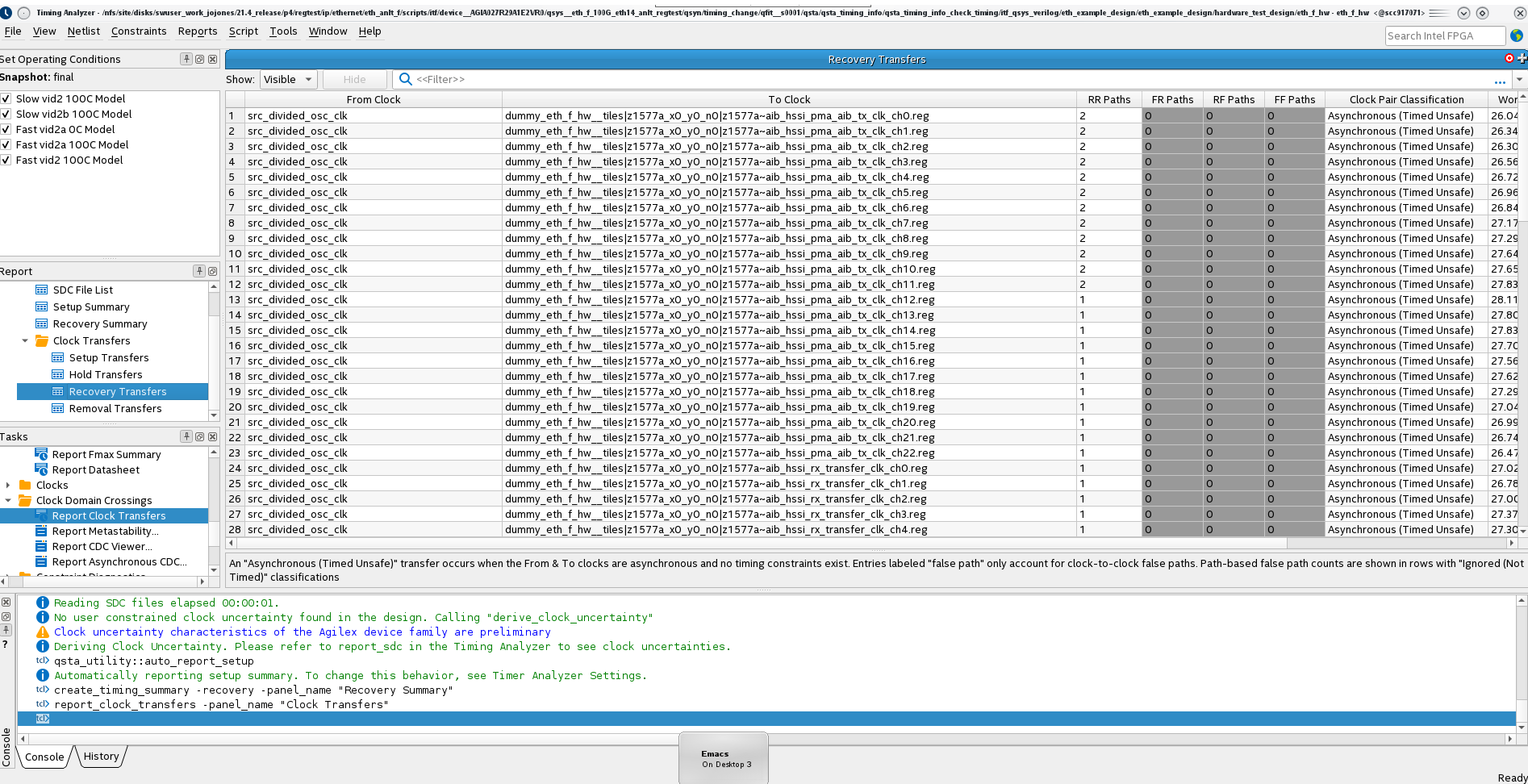

) Lihat laporan penyeberangan domain clock untuk melihat jalur waktu yang tidak dibatasi.

Ini menunjukkan jalur waktu yang tidak dibatasi sebagai Asynchronous (Timed Unsafe). Meskipun Penganalisis Waktu tidak melaporkan galat waktu untuk jalur ini, mereka harus dibatasi sehingga tidak disertakan dalam analisis waktu.

Ini menunjukkan jalur waktu yang tidak dibatasi sebagai Asynchronous (Timed Unsafe). Meskipun Penganalisis Waktu tidak melaporkan galat waktu untuk jalur ini, mereka harus dibatasi sehingga tidak disertakan dalam analisis waktu. -

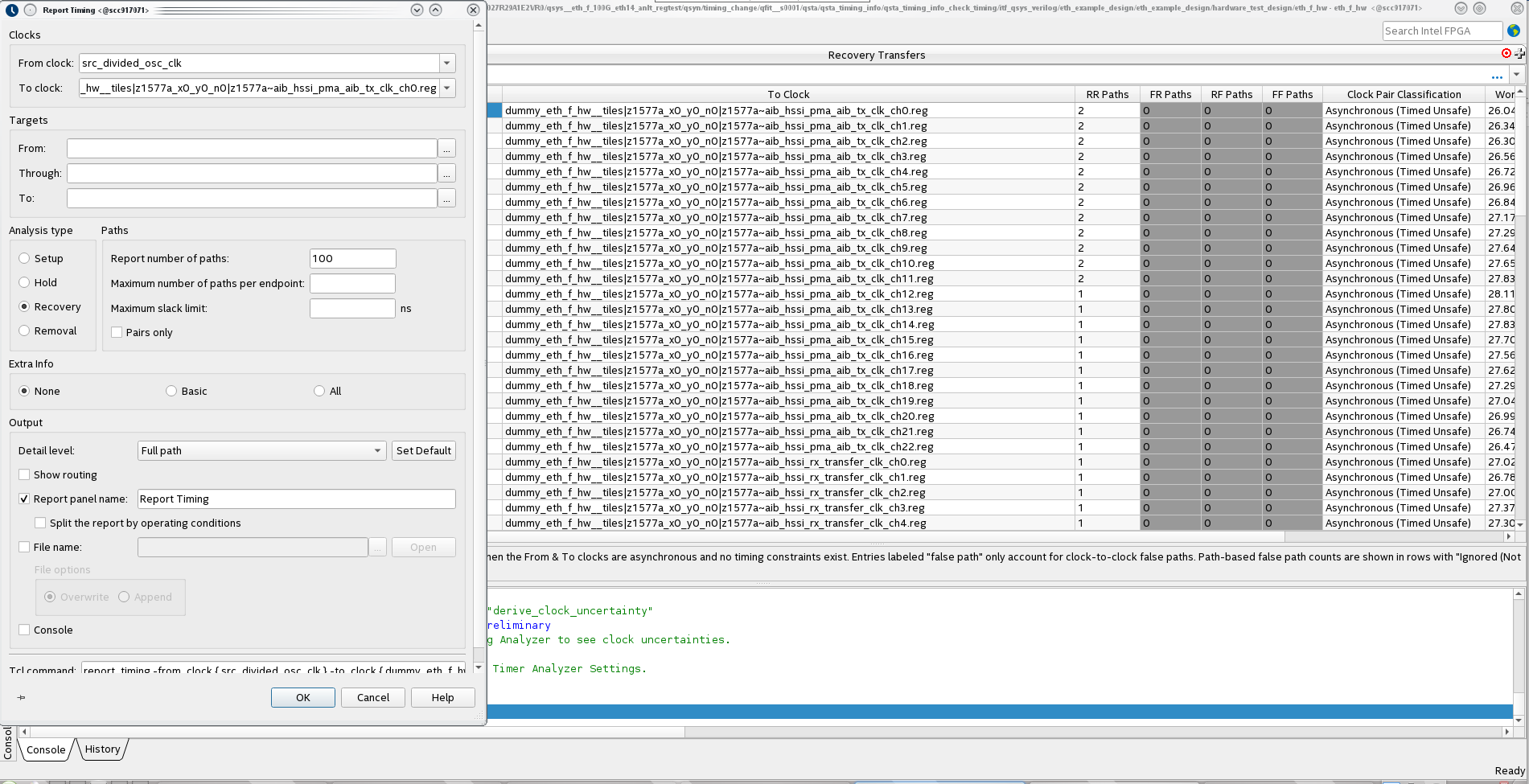

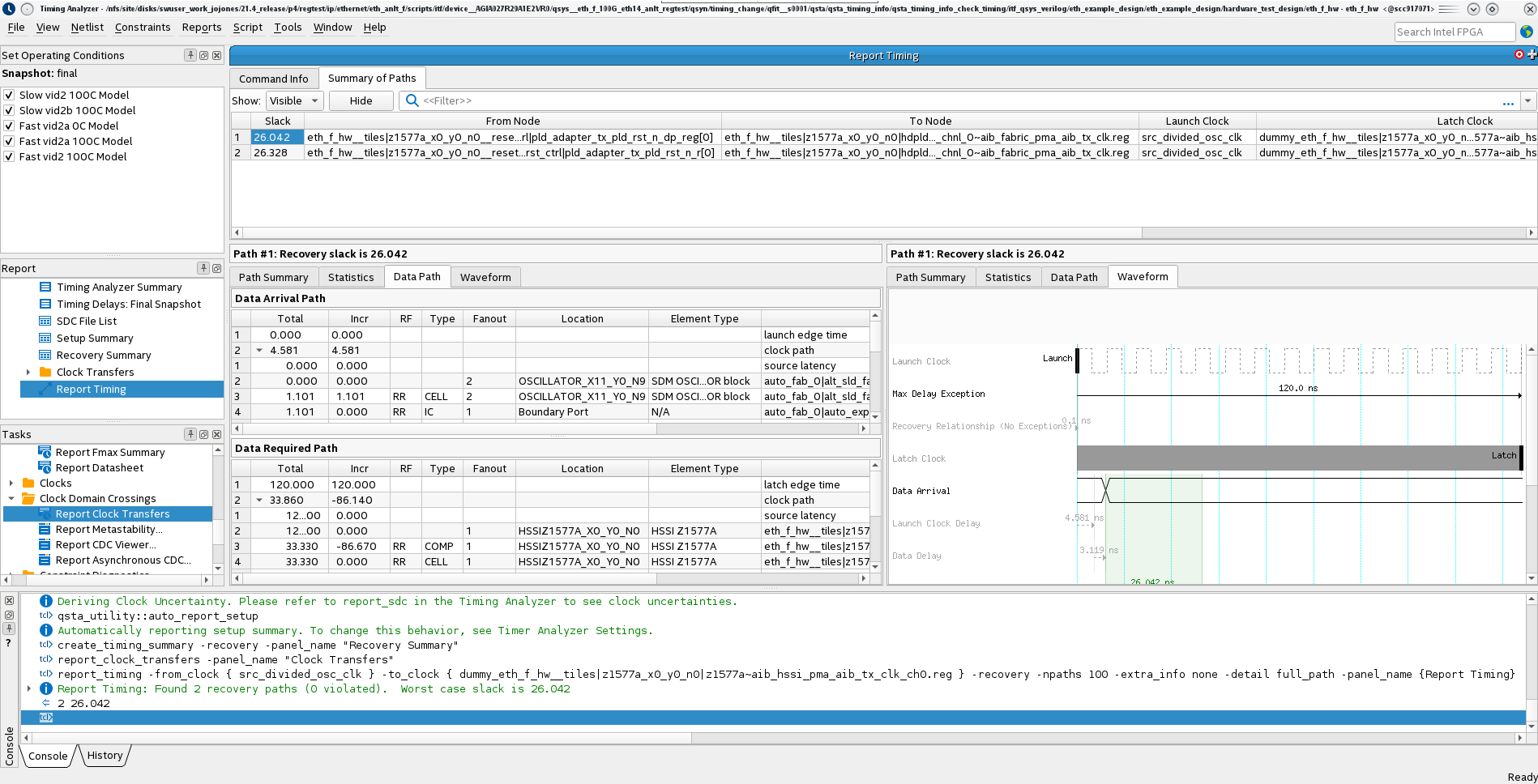

) Untuk mengatur batasan pada jalur ini, pilih salah satunya, klik kanan mouse, dan pilih Waktu Laporan. Opsi bawaan untuk laporan seperti yang ditunjukkan sudah cukup.

-

) Klik OK. Laporan Waktu akan dihasilkan.

-

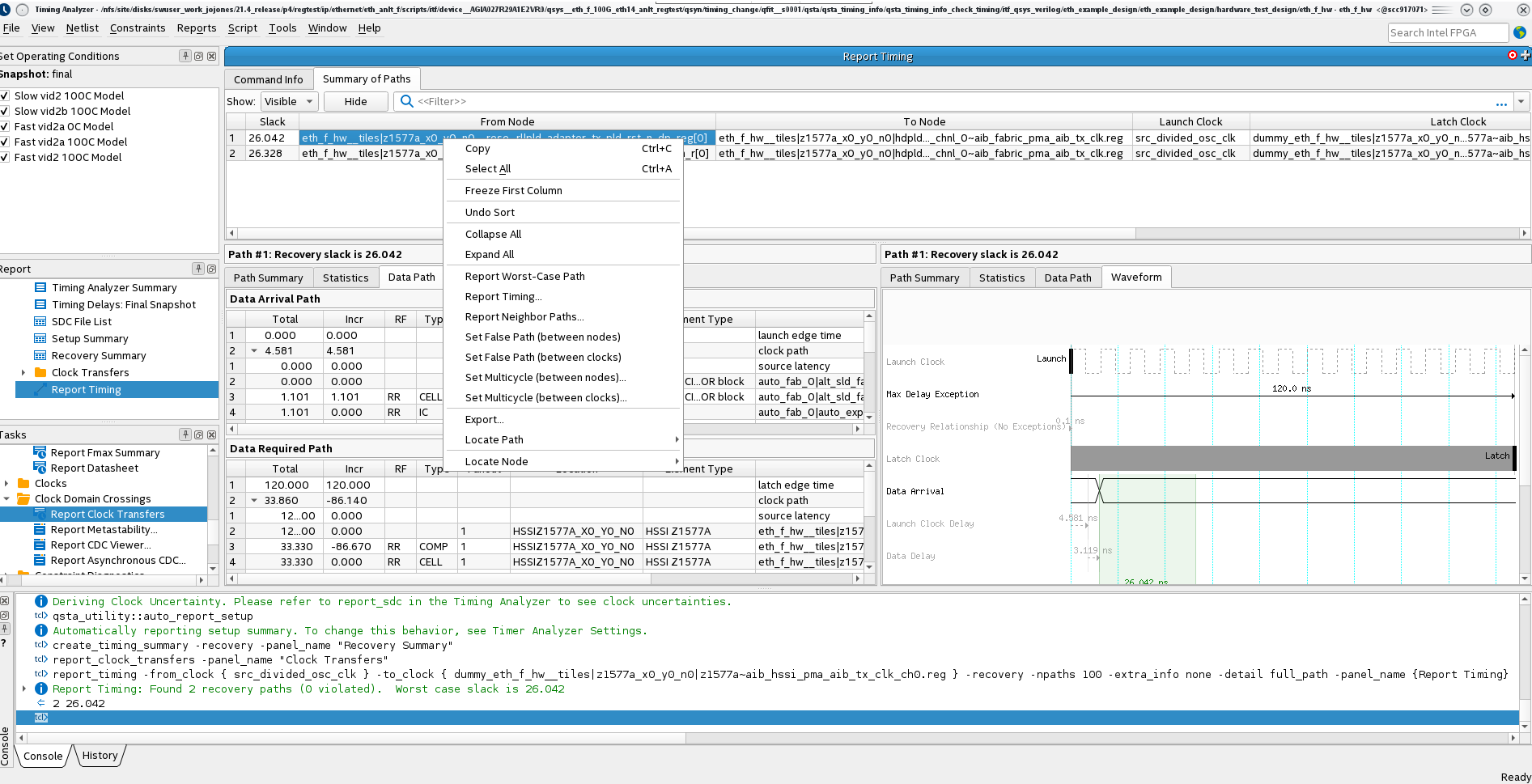

) Untuk membatasi jalur sebagai Jalur Palsu, artinya jalur tersebut tidak akan lagi disertakan dalam analisis waktu, klik kanan di mana saja pada jalur dan pilih Set False Path (antara node)....

-

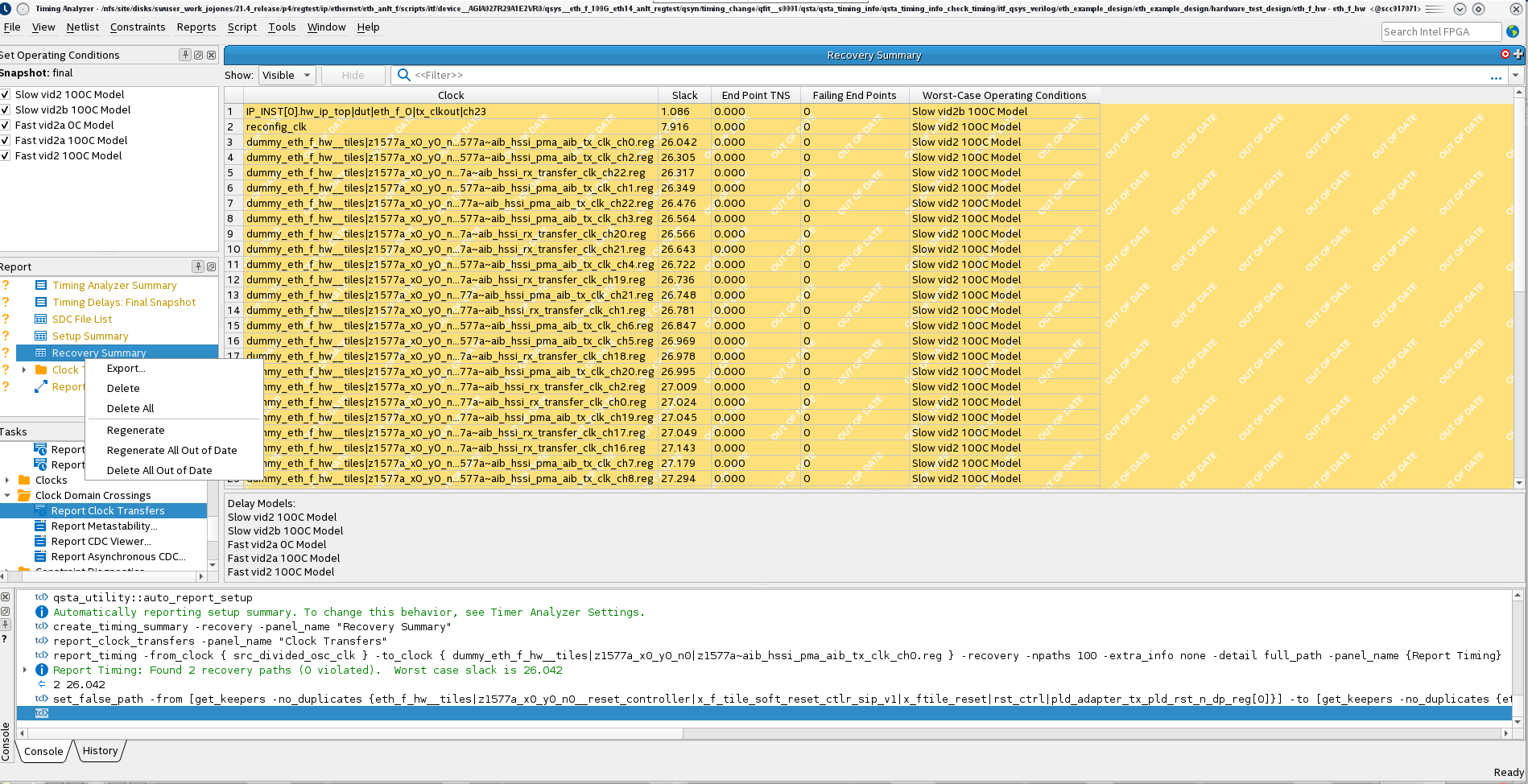

) Untuk meregenerasi laporan waktu, klik kanan pada salah satu laporan yang ditunjukkan di jendela Laporan dan pilih Regenerasi Semua Yang Sudah Tidak Berlaku.

Setelah Anda meregenerasi laporan yang sudah tidak berlaku, Anda akan melihat bahwa jalur waktu yang dibatasi tidak lagi muncul di laporan ringkasan. Ini karena Anda telah membatasi Penganalisis Waktu untuk tidak menganalisis jalur palsu tersebut.

Setelah Anda meregenerasi laporan yang sudah tidak berlaku, Anda akan melihat bahwa jalur waktu yang dibatasi tidak lagi muncul di laporan ringkasan. Ini karena Anda telah membatasi Penganalisis Waktu untuk tidak menganalisis jalur palsu tersebut. -

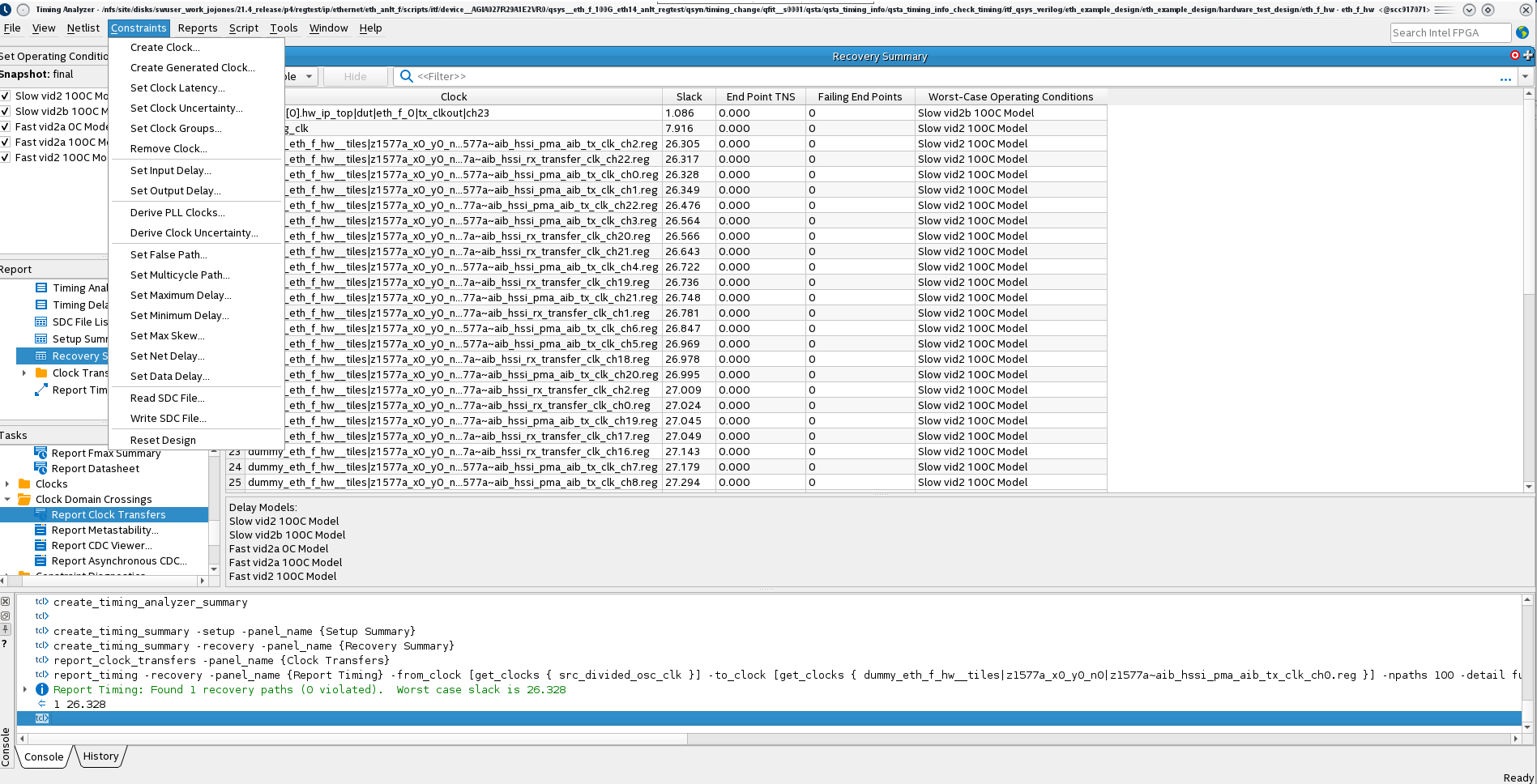

) Ulangi ini untuk semua jalur yang ingin Anda batasi. Setelah selesai, simpan semua perubahan yang telah Anda buat di berkas .sdc baru dengan memilih Tulis Berkas SDC... dari menu Batasan .

Anda dapat memilih nama dan lokasi berkas .sdc yang akan ditulis.

File .sdc yang dihasilkan akan mencakup semua batasan dari file .sdc yang awalnya dibaca untuk desain ditambah batasan baru yang telah Anda tambahkan.

Anda dapat menambahkan berkas .sdc ini ke proyek Perangkat Lunak Prime Intel Quartus Anda untuk kompilasi di masa depan.

Masalah ini dijadwalkan akan diperbaiki dalam rilis Intel Quartus Perangkat Lunak Edisi Prime Pro di masa mendatang.