Masalah Kritis

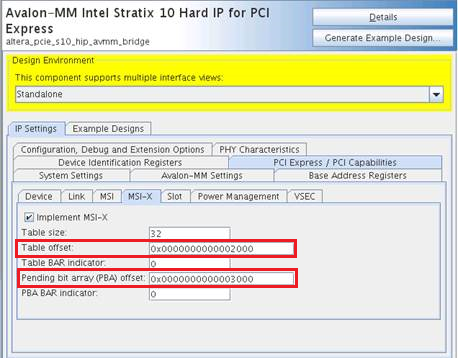

Karena masalah dalam perangkat lunak Intel® Quartus® Prime Edisi Pro versi 19.2 atau sebelumnya, parameter MSI-X di bawah ini yang ditunjukkan dalam GUI tidak cocok dengan param dalam RTL yang dihasilkan.

- Offset tabel

- Offset bit array (PBA) yang tertunda

Untuk mengatasi masalah ini, modifikasi parameter di bawah ini di "altera_pcie_s10_hip_avmm_bridge.v".

parameter [28:0] pf0_pci_msix_pba_offset = 29'h2000 ,

parameter [28:0] pf0_pci_msix_table_offset = 29'h3000

Masalah ini telah diperbaiki pada perangkat lunak Intel® Quartus® Prime Pro versi 19.3 dan seterusnya.